- Published on

MIO vs EMIO

- Authors

- Name

- JaeHyeok CHOI

- none

MIO vs EMIO

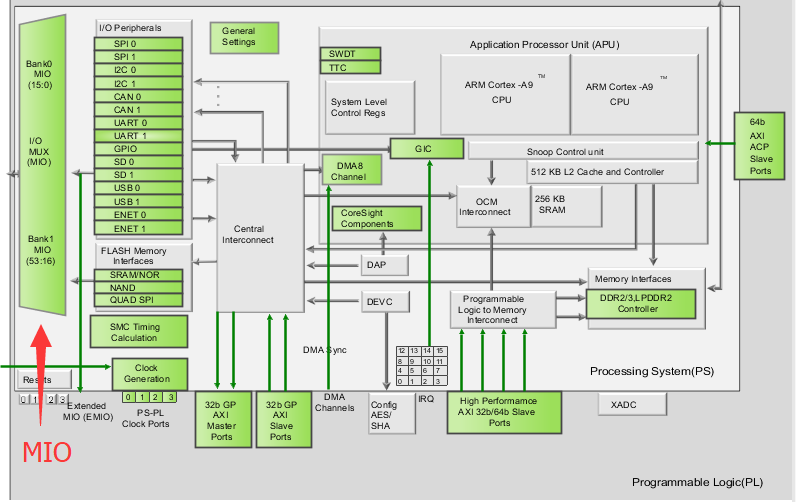

주로 Zynq SoC 같은 FPGA + ARM Cortex-A 프로세서가 통합된 시스템에서 사용되는 두 가지 주요 I/O 인터페이스이다. 이들은 프로세서 시스템 PS와 FPGA 로직 간의 I/O 핀을 어떻게 사용할지 결정하는 데 중요한 개념이다.

MIO (Multiplexed I/O)

MIO는 PS에 직접 연결된 I/O 이다. 이 핀들은 프로세서에서 관리하는 고정된 핀으로 일반적인 주변 장치 (UART, I2C, SPI, GPIO 등)의 인터페이스로 사용된다.

✅ 특징: 프로세서(ARM Cortex-A)에서 직접 제어 PS와 연결된 고정 핀을 사용 빠르고 간단한 인터페이스 핀 수가 제한적 (일반적으로 54개 핀) 주로 저속 주변 장치와 통신할 때 사용 (예: UART, I2C, SPI) ✅ 예시: UART0, I2C, SPI 등은 MIO 핀을 통해 외부 장치와 통신 Zynq-7000 시리즈에서는 최대 54개의 MIO 핀이 제공됨 ✅ 장점: 설정이 간단하고 빠른 데이터 전송이 가능 FPGA fabric을 통하지 않으므로 레지스터 레벨에서 직접 제어 가능

EMIO (Extended Multiplexed I/O)

EMIO는 FPGA fabric을 통해 연결되는 확장형 I/O이다. MIO 핀이 부족하거나 더 많은 주변 장치와 통신해야 할 때 사용되며 이 핀은 PS와 FPGA 사이의 AXI 인터커넥트를 통해 연결된다.

✅ 특징: PS가 FPGA fabric을 통해 I/O를 제어 FPGA의 모든 I/O 핀을 사용 가능 MIO 핀 수가 부족할 때 유용 PS에서 GPIO, UART, I2C, SPI 등의 주변 장치를 FPGA 내부에서 라우팅하여 사용 유연하게 고속 I/O 핸들링 가능 ✅ 예시: 프로세서에서 제어하는 GPIO가 MIO 핀을 초과하면 EMIO를 통해 FPGA의 I/O 핀에 연결 FPGA 로직을 통해 맞춤형 프로토콜을 구현한 후 PS와 통신 ✅ 장점: FPGA 핀 수를 자유롭게 확장 가능 고속 데이터 통신에 적합 FPGA 내의 커스텀 로직과 통합 가능

MIO vs EMIO 비교 표

| 구분 | MIO | EMIO |

|---|---|---|

| 연결 방식 | PS에 직접 연결 | FPGA fabric을 통해 연결 |

| 핀 개수 제한 | 최대 54개 | 제한 없음 (FPGA 핀 전체 사용 가능) |

| 유연성 | 낮음 | 높음 |

| 속도 | 빠름 | 고속 커스텀 통신 가능 |

| 사용 예시 | UART, I2C, SPI 등 | 고속 GPIO, FPGA 커스텀 인터페이스 |

사용 환경

MIO

- 기본적인 UART, I2C, SPI 등의 저속 주변 장치와 통신시

- 핀 수가 제한적이기 때문에 적은 수의 장치와 통신

EMIO

- MIO 핀이 부족할 때

- FPGA fabric을 활용한 커스텀 로직을 사용

- 고속 GPIO, 특정 신호 라우팅 필요할 때

AXILNX 에서의 MIO 테스트

AX7010의 MIO에는 2개의 BANK가 있고 BANK0에는 16개의 핀이 있으며, BANK1에는 38개의 핀이 있어 총 54개의 핀이 있다.

원리

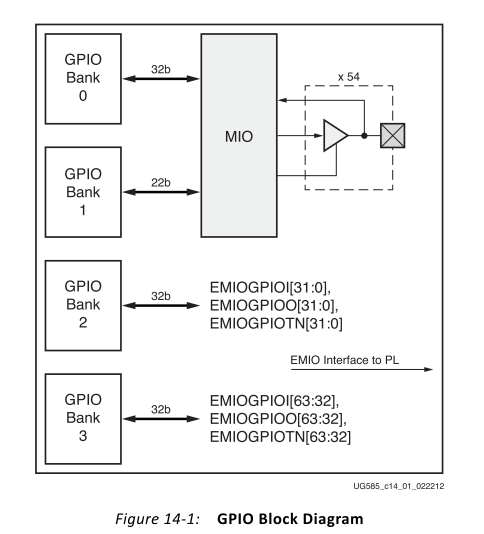

먼저 GPIO의 BANK 분포를 이해해보자. UG585 문서의 GPIO 장에서 GPIO에는 4개의 BANK가 있음을 알 수 있다. BANK0은 32개의 신호를 제어하고 BANK1은 SPI, I2C, USB, SD 등과 같은 PS 측 주변 장치 인터페이스인 총 54개의 MIO핀인 22개의 신호를 제어하며 BANK2 및 BANK3은 총 64개의 PL측을 제어할 수 있다. 핀, 각 그룹에는

- 입력 EMIOGPIOI

- 출력 EMIOGPIOO

- 출력 활성화 EMIOGPIOTN

세 가지 신호가 있으며, 이는 tri-state 게이트와 유사하며 총 192개의 신호이다. PL측 핀에 연결하여 PS를 통한 신호를 제어할 수 있다.

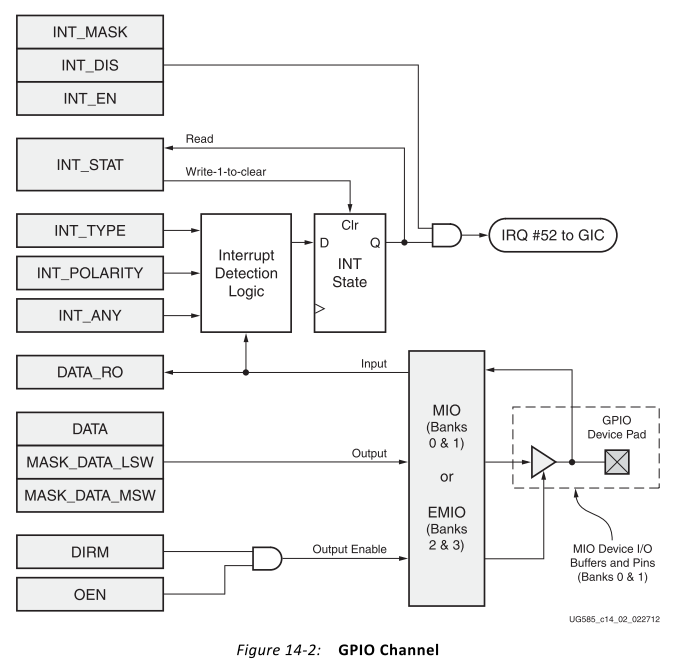

GPIO 제어 블록 다이어그램

GPIO와 GPIO 인터럽트 블록 다이어그램