- Published on

PCIe explained

- Authors

- Name

- JaeHyeok CHOI

- none

PCIE Explained

PCIe (Peripheral Component Interconnect)

주변 장치를 CPU 및 메모리와 연결하는데 사용되는 표준 인터페이스.

2024년까지 PCIe gen 7까지 spec이 지정되어 있으며 사용 장치는 PCIe gen 5까지 출시되어 있다.

PCIe Link

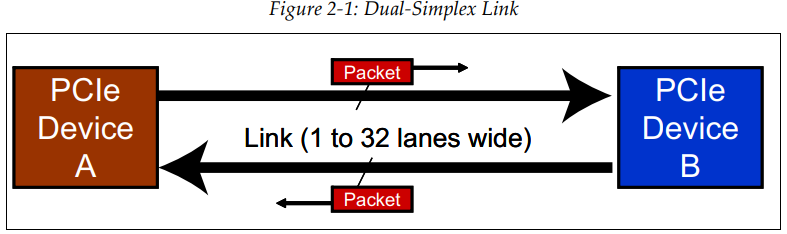

PCIe는 point-to-point serial bus 이며, link는 하나 이상의 lane으로 구성이 된다. 또한 PCIe lane은 동시에 양방향 송수신이 가능한 full-duplex 연결이므로 하나의 lane은 Tx와 Rx 부분의 wire로 구성되어 있다. 그래서 하나의 lane은 2개의 wire라고 생각할 수 있으나, PCIe는 differential signaling을 사용하기 때문에 Tx와 Rx는 각각 2개의 wire를 가지게 된다. 즉, 하나의 PCIe lane은 총 4개의 wire로 구성된다.

왜 PCIe에서 serial bus를 사용할까?

Serail bus가 가지는 장점

간소화된 신호 처리 serial bus는 data 전송을 위해 단일 또는 소수의 data line만 사용할 수 있다. 병렬 데이터에 비해 물리적 연결이 간소화되어 설계가 단순하고 비용적인 측면에서 더 효율적이다.

높은 데이터 전송 속도 PCIe와 같은 serial interface는 높은 데이터 전송 속도를 지원한다. serial com 에서는 data가 연속적인 bit stream으로 전송되므로 클럭 속도를 높일 수 있기 때문이며 이는 동일한 클럭 속도에서 데이터를 더 빠르게 전송할 수 있다.

신호 무결성 향상 신호 간섭 및 전자기 간섭 문제를 줄일 수 있다. 각 신호 하인이 별도로 보호되고 더 적은 수의 신호선을 사용하기 때문에 간섭이 그만큼 줄어들어 안정적인 데이터 전송을 가능케 한다.

스케일링 용이성 PCIe는 라인수를 증가시키거나 줄이는 것이 비교적 간단하다. 이를 통해 시스템 요구사항에 맞춰 유연하게 대역폭을 조정할 수 있다.

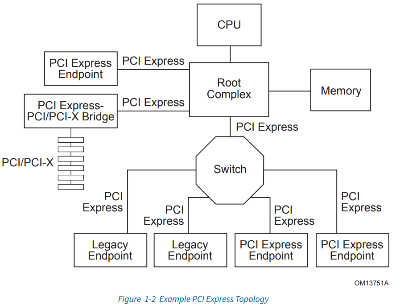

PCIe Topology

Root Complex

Root Complex는 CPU 및 메모리와 직접 연결되는 PCIe 시스템의 주요 요소이다. 이는 시스템의 host bus interface를 제공, PCIe topology 내의 다른 모든 구성요소와 통신을 관리한다. root complex는 하나 이상의 PCIe 포트를 포함, 이 포트들은 다른 PCIe device 혹은 PCIe switch로 연결된다. 대표적으로 intel 에서는 intel 마더보드의 칩셋 구성요소인 PCH(Platform Controller Hub)를 통해 CPU와 다른 시스템 부품 사이의 통신을 지원한다.

Switch

PCIe switch는 다수의 PCIe device 간의 packet을 routing 하는 역할을 한다. 이는 network switch와 유사하게 작동하며 여러 endpoint device 또는 다른 switch 와의 연결을 확장(fan-out) 하는데 사용된다.

Bridge

PCIe bridge는 서로 다른 버스 표준을 연결하는데 사용된다. PCI-to-PCIe bridge는 기존 PCI bus 기반 디바이스를 PCIe topology에 통합될 수 있도록 한다. 이 브릿지는 data 포맷과 전송 프로토콜 차이를 해결하며 두 다른 버스 시스템 간의 호환성을 보장한다.

Endpoint

Endpoint device는 PCIe topology의 최종 사용자 디바이스로 GPU, NIC, SSD 등이 해당한다. 각 엔드포인트는 PCIe interface를 통해 데이터를 송수신할 수 있는 독립적인 기능을 가지고 있으며, 이들은 root complex 또는 switch를 통해 시스템의 다른 부분과 통신한다.

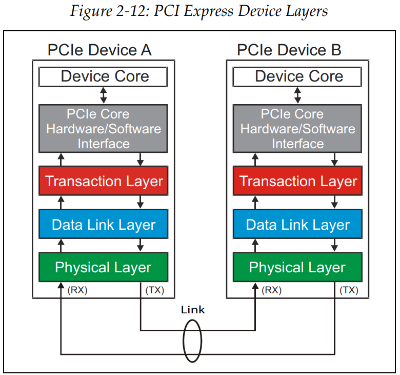

PCIe Layer

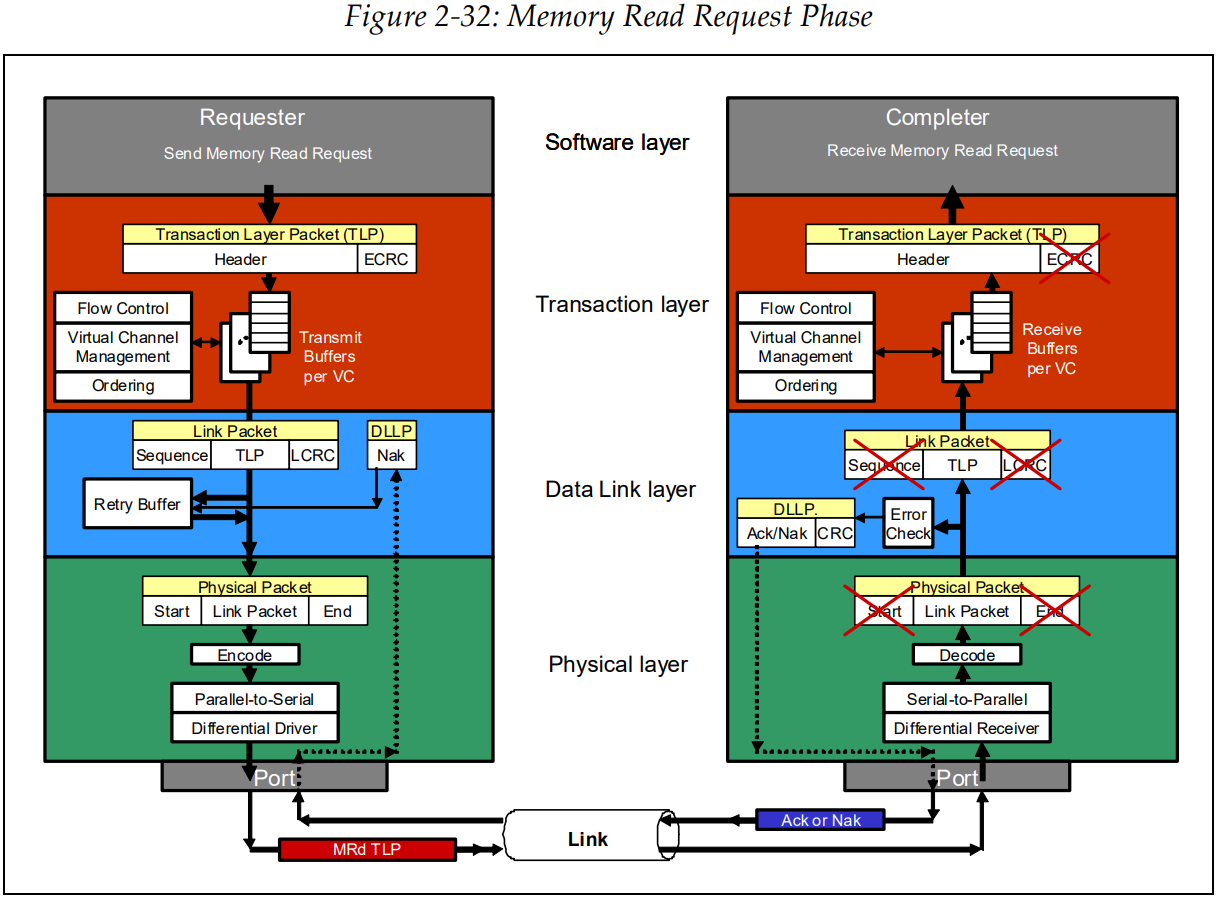

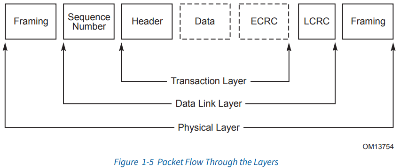

PCIe architecture는 계층적 구조로 되어 있으며 이는 각 계층이 특정 기능을 수행하도록 설계되어 있다. 주요 계층은 transaction layer, data link layer, physical layer 이며 역할은 다음과 같다.

Transaction Layer

이는 data transaction의 생성 및 관리를 담당한다. 이 계층에서는 data packet(TLPs)를 구성하고 데이터 전송을 위한 address 지정, 오류 검출, transaction routing 등을 수행한다. transaction 계층은 read, write 그리고 message 전송과 같은 다양한 transaction 유형의 요청을 생성할 수 있으며, 이러한 요청을 data link layer로 전달하여 데이터 전송이 이루어지도록 한다.

Data Link Layer

주요 기능은 데이터의 안정적인 전송을 보장하는 것이다. 이 계층은 전송된 데이터의 무결성을 검증하고 오류검충 (LCRC) 및 수정 (Retry)을 수행한다. 또한 data link layer packet (DLLPs)은 packet의 전송을 확인하고 필요한 경우 재전송을 관리한다. 이 계층은 transaction layer와 physical layer 사이의 인터페이스 역할을 하며, flow control과 packet의 ordering을 담당하여 data의 안정적인 전송을 돕는다.

Physical Layer

실제 data 전송을 담당하는 Hardware 계층이다. 이 계층에서는 전기 신호를 처리하고 data를 전기적 신호로 변환, PCIe device 간의 실제적인 data 전송을 가능하게 한다. physical layer는 data link layer로 부터 받은 정보를 serial data stream으로 encoding 하고 전송하며 수신된 data를 다시 decoding한다. 또한 physical layer는 serial 통신에서 발생할 수 있는 clock recovery 및 data 정렬과 같은 기능도 제공한다.

메모리 Read 요청 예시