- Published on

HDMI HW Specification

- Authors

- Name

- JaeHyeok CHOI

- none

HDMI

하드웨어

개발 보드는 HDMI 인코딩 칩을 사용하지 않으며 FPGA의 3.3V 차동 IO를 HDMI 커넥터에 직접 연결하여 24비트 RGB 인코딩을 완료하여 TMDS 차동 신호를 출력한다.

TMDS(Transition Minimized Differential Signaling) 원리

HDMI는 DVI - TMDS와 동일한 전송 원리를 사용, 차동 신호 전송을 최소화한다.

TMDS 전송 시스템은 송신단과 수신단의 두 부분으로 나뉜다. TMDS 송신기는 HDMI 인터페이스로부터 RGB 신호를 나타내는 24비트 병렬 데이터를 수신한다. (TMDS는 각 픽셀의 RGB 3원색을 8비트로 인코딩한다.) 그 후 이 데이터를 인코딩하고 병렬/직렬 변환한 다음 세 개의 RGB 신호를 나타내는 데이터를 독립적인 전송 채널에 할당하여 보낸다. 수신단은 송신단으로부터 직렬 신호를 수신하고 이를 디코딩하여 직렬/병렬로 변환한 후 디스플레이의 제어단으로 보내게 된다. 동시에 클럭 신호도 수신되어 동기화를 달성한다.

각 TMDS 링크에는 RGB 신호 전송을 위한 3개의 데이터 채널과 클럭 신호 전송을 위한 1개의 채널이 포함되어 있다. 각 데이터 채널은 코딩 알고리즘을 사용, 8비트 오디오 및 비디오 데이터 전송을 최소화하고 DC 균형을 이루는 10비트 데이터로 변환한다. 이를 통해 데이터 전송 및 복구의 신뢰성이 더욱 높아진다. 최소화된 전송 차동신호는 원래의 8비트 신호 데이터를 XOR 등의 논리 알고리즘을 통해 10비트로 변환하고 DC 밸런스에 대응하는데 사용된다.

일반적으로 HDMI 전송의 인코딩 형식에는 비디오 데이터, 제어 데이터 및 데이터 패킷이 포함된다. (데이터 패킷에는 오디오 데이터와 오류 수정 코드 등과 같은 추가 정보 데이터가 포함됨.) TMDS의 각 채널에는 전송 중에 2비트 제어 데이터, 8비트 비디오 데이터 또는 4비트 데이터 패킷이 포함되어야 한다. HDMI 정보 전송 과정은 비디오 데이터 전송 주기, 제어 데이터 전송 주기, 데이터 아일랜드(?) 전송 주기의 세 단계로 나눌 수 있으며, 이는 각각 위의 세 가지 데이터 유형에 해당한다.

TMDS 에 사용되는 기술

- 전송 최소화

8비트 데이터를 인코딩하고 DC 밸런싱을 수행하여 10비트의 최소화된 데이터를 얻는다. 이는 중복 비트를 증가시키고 전송 링크의 더 높은 대역폭을 요구하지만 실제로는 이 알고리즘을 통해 얻은 10비트 데이터를 처리한다. 이를 통해 동축 케이블의 전송 신뢰성이 향상된다.

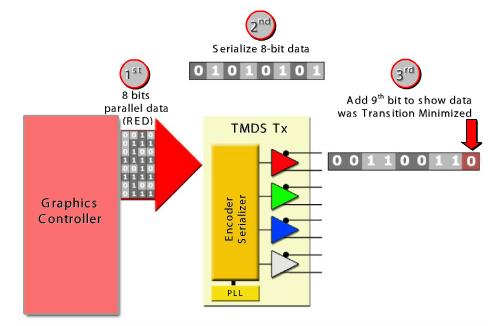

아래 그림은 8비트 병렬 RED 데이터의 인코딩 및 병렬/직렬 변환의 예시이다.

1단계: 8비트 병렬 RED 데이터를 TMDS 송신기로 전달 2단계: 병렬/직렬 변환 3단계: 전송 처리를 최소화하고 인코딩 프로세스인 9번째 비트를 추가. 데이터의 9번째 비트를 인코딩 비트라고 한다.

- DC 밸런싱

DC 밸런싱은 인코딩 프로세스 중 채널의 DC 오프셋이 0이 되도록 보장하는 것을 의미한다. 이 방법은 원래 9비트 데이터 뒤에 10번째 비트의 데이터를 추가하는 것이다. 이런 방식으로 전송된 데이터는 DC 밸런싱을 이루게 되어 전송 라인에 대한 신호의 EMI 간섭을 줄이고 신호 전송의 신뢰성을 향상시킨다.

- 차동신호

TMDS 차동 전송 기술은 두 핀 사이의 전압 차이를 이용해 신호를 전송하는 기술이며, 전송된 데이터의 값(0 또는 1)은 양극 및 음극 극성과 두 핀 사이의 전압 크기에 따라 결정된다. 즉, 신호를 전송하는 데 두 개의 와이어가 사용되며, 한 와이어는 원래 신호를 전송하고 다른 와이어는 원래 신호의 반대 신호를 전송한다. 이러한 방식으로 수신측에서는 한 라인의 신호를 다른 라인의 신호에서 빼 전자기 간섭을 차폐할 수 있으며 이에따라 올바른 신호를 얻을 수 있다. (개인적으로 RS422 등의 차동 신호 규격과 스펙은 아주 다르지만 유사하다.) 또한, 수신 측 디스플레이의 해상도 및 기타 디스플레이 기능을 나타내는 확장 디스플레이 식별 데이터(EDID)를 읽는 데 사용되는 신호선인 디스플레이 데이터 채널 (DDC)이 있다. DDC 회선은 HDCP(고대역폭 디지털 콘텐츠 보호, 고대역폭 디지털 콘텐츠 보호 기술)가 탑재된 송신 장치와 수신 장치 간의 비밀번호 키 인증에도 사용된다.

비디오 타이밍 표준

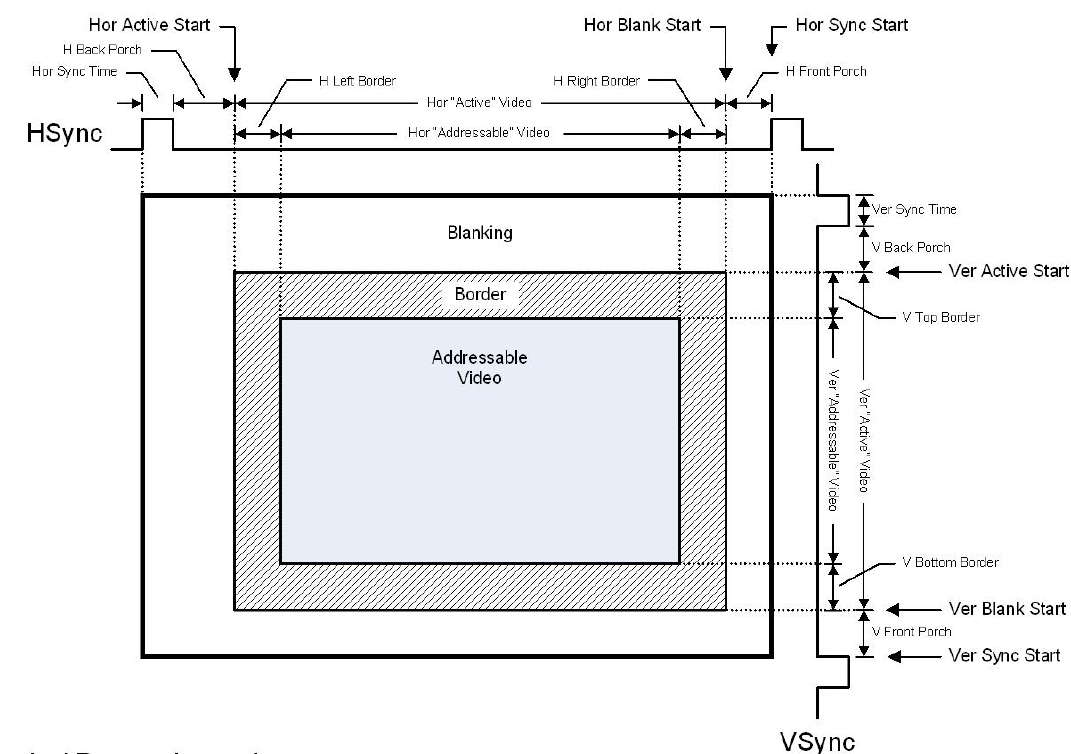

HDMI 디스플레이 스캐닝 방식은 화면의 왼쪽 상단 모서리에 있는 한 지점에서 시작, 오른족으로 한 지점씩 스캔한다. 각 라인이 스캔된 후 전자 빔은 화면 왼쪽의 다음 라인의 시작 위치로 돌아간다. 이 기간 동안 CRT는 각 라인의 끝에서 수평 동기화 신호를 사용해 모든 라인을 스캔하고 프레임을 형성하며 필드 동기화를 위해 사용한다. 필드 블랭킹(?)을 수행하고 다음 프레임을 시작하는 동안 스캐닝은 화면의 왼쪽 상단으로 돌아간다.

한 라인의 스캐닝을 완료하는 데 걸리는 시간을 수평 스캐닝 시간이라고 하며, 그 역수를 라인 주파수한다. 한 프레임(전체화면) 스캐닝을 완료하는데 걸리는 시간을 수직 스캐닝이라고 하며, 그 역수를 필드 주파수라고 한다. 한 화면을 새로 고치는 빈도는 60Hz, 75Hz 등이 있으며, 표준 디스플레이 필드 주파수는 60Hz이다.

클록 주파수: 1024 x 768 @59.94Hz(60Hz)를 예로 들면, 각 필드는 806개의 라인 기간에 해당하며 그 중 768개는 디스플레이 라인이다. 각 디스플레이 라인에는 1344개의 클럭 포인트가 포함되어 있으며, 그 중 1024개의 포인트가 유효 디스플레이 영역이다.

그림) 필요한 클록 주파수: 806 * 1344 * 60 약 65MHz

비디오 타이밍

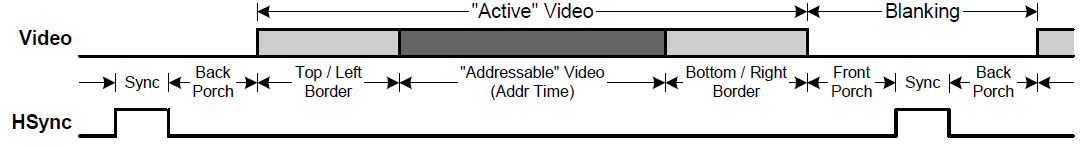

VGA 스캐닝, 기본 요소는 라인 스캐닝이며 여러 라인이 프레임을 형성한다. 다음 그림은 라인의 타이밍을 보여준다. 여기서 "활성" 비디오는 비디오 라인의 유효 픽셀, 위쪽/왼쪽 테두리 및 아래쪽/오른쪽 테두리이다. 둘다 대부분의 해상도에서 클락은 0이다. "Blanking"은 라인의 동기화 시간이며 "Blanking" 시간 + "Active" 비디오 시간은 라인의 시간이다. "Blanking"은 "Front Porch", "Sync" 및 "Back Porch"의 세 부분으로 구분된다.

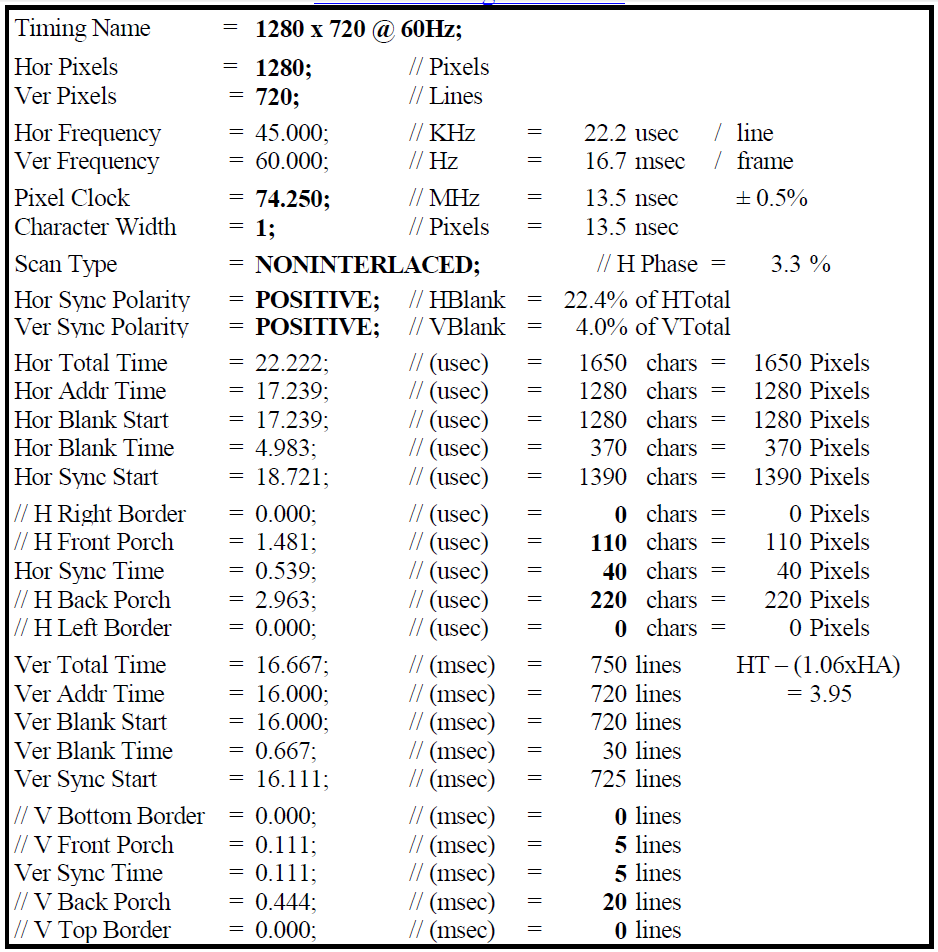

다음은 720p의 타이밍 매개변수이다.

비디오 타이밍 표준 해석

Blanking

화면의 한 프레임이 끝나고, 다음 프레임으로 넘어갈 때 필요한 라인이다. 화면 상에는 보이지 않으나 디스플레이 장치가 다음 프레임을 준비할 시간을 제공하는 '비활성 라인'이다.

- 활성 라인: 화면에 보이는 라인으로써 위 예제에서 768개의 라인을 의미한다.

- 수직 블랭킹 라인 (VBP, VFP, VSync): 보이지 않는 라인, HDMI 표준에서 정해진 규격이 있다. (32개)

- 수평 블랭킹 라인

- 프론트 포치 FP: 라인 시작 전 준비 시간

- 동기 신호: 동기화를 위한 클럭

- 백 포치 BP: 라인 끝난 후의 안정화 시간