- Published on

Vivado Basic Tutorial

- Authors

- Name

- JaeHyeok CHOI

- none

Vivado Basic Tutorial

ARM 사용하기

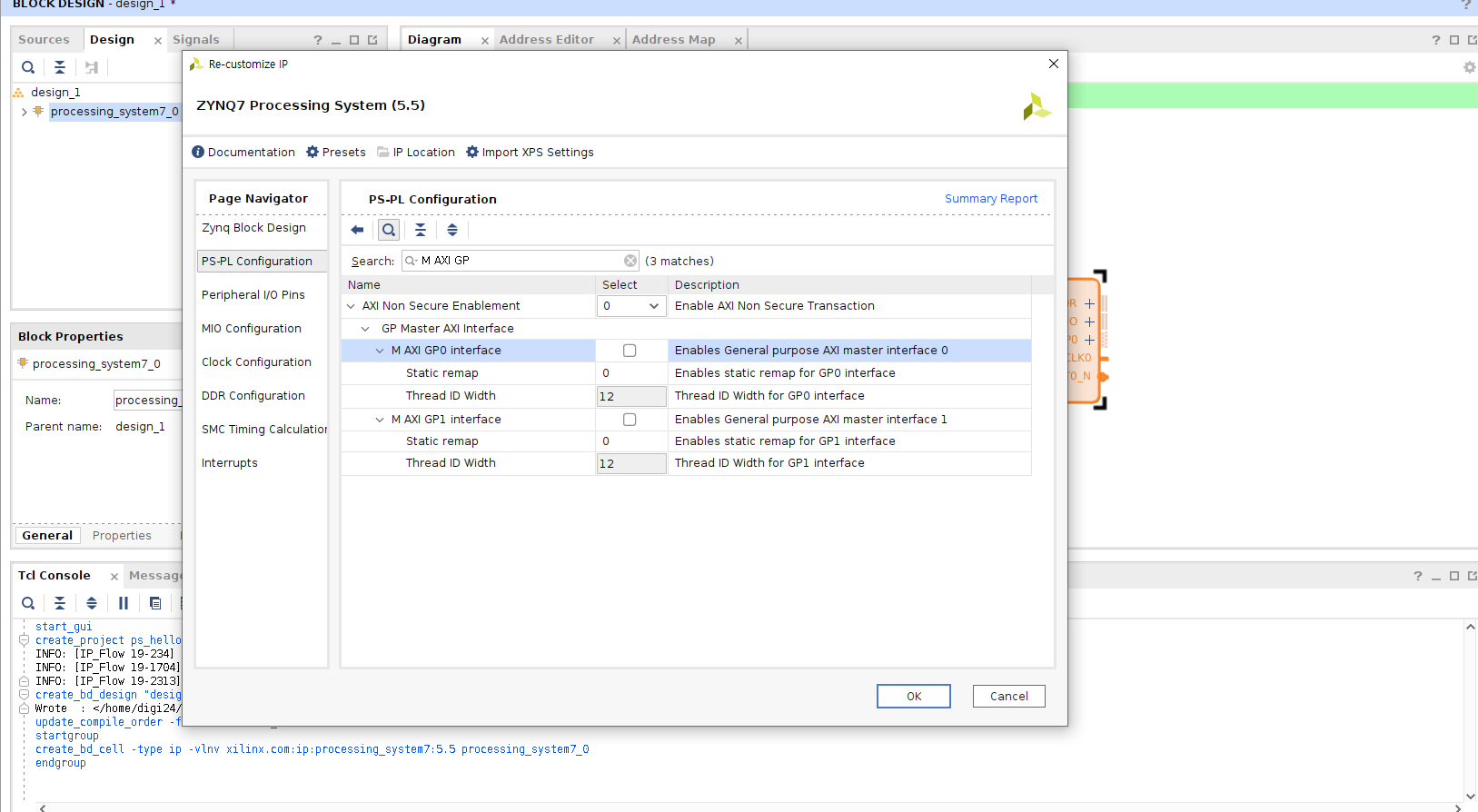

Add ip를 사용하여 ZYNQ 프로세서 블록 다이어그램을 등록해준 후, 더블 클릭하여 configuration에 들어간다.

PS-PL Configuration 에서 M AXI GP0 인터페이스를 disable 한다. 이를 취소하면 이 인터페이스는 PL 측의 AXI 인터페이스 주변 장치를 확장할 수 있으므로 PL이 PS와 상호작용하기 위해선 AXI 버스 프로토콜을 따라야 한다.

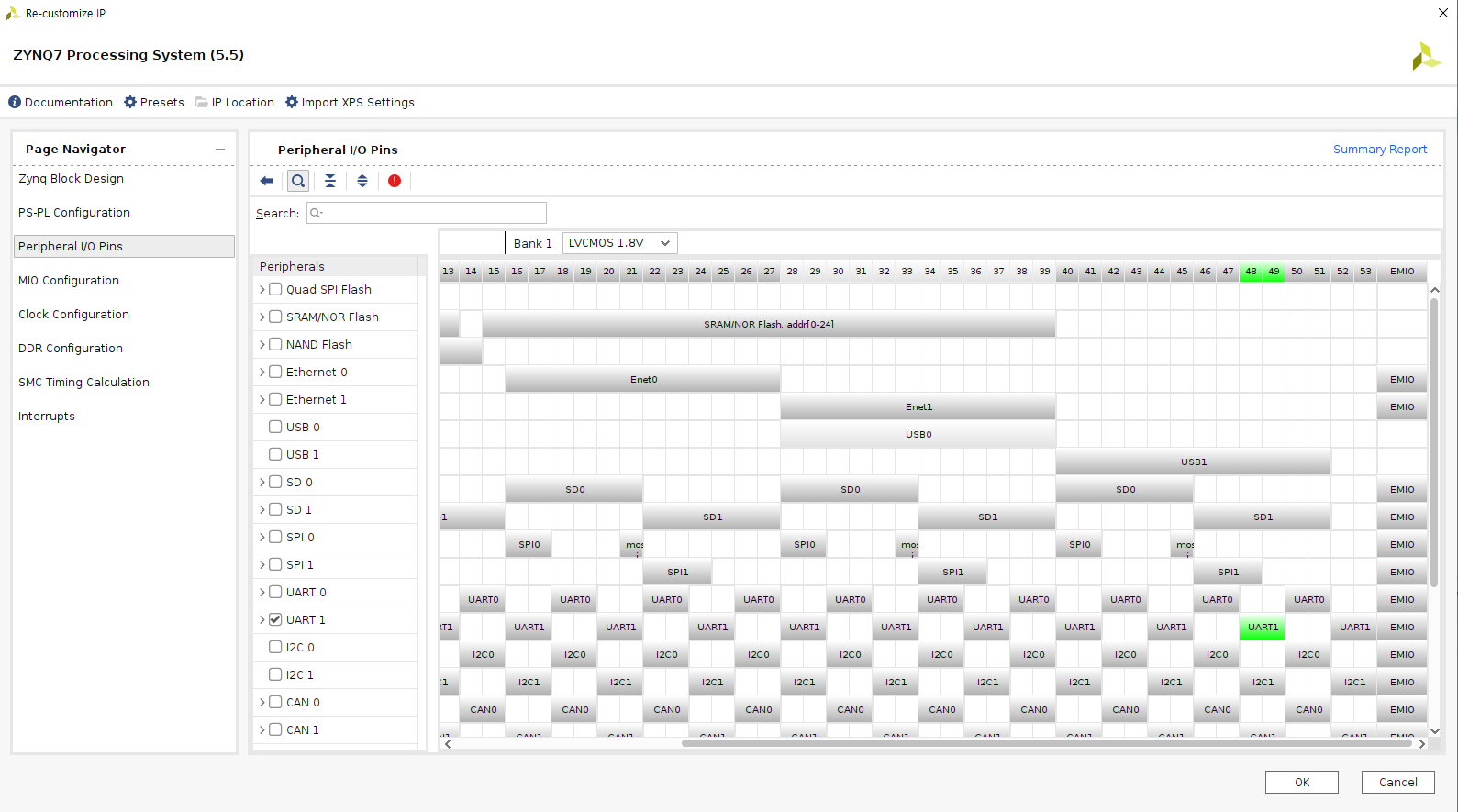

UART Configuration

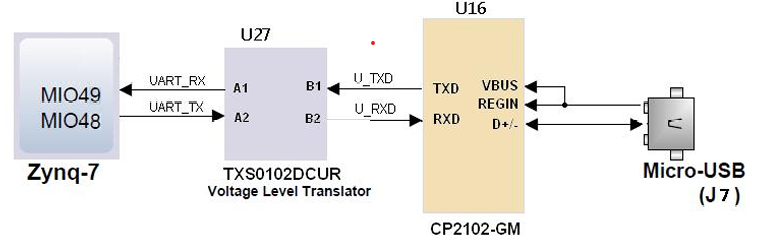

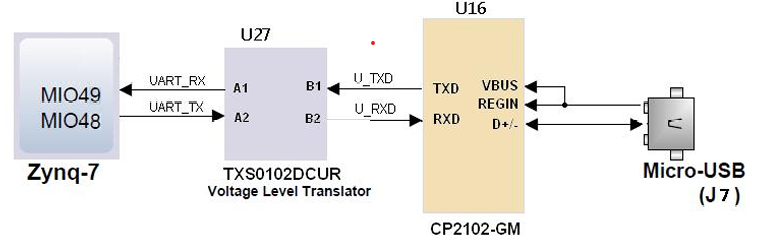

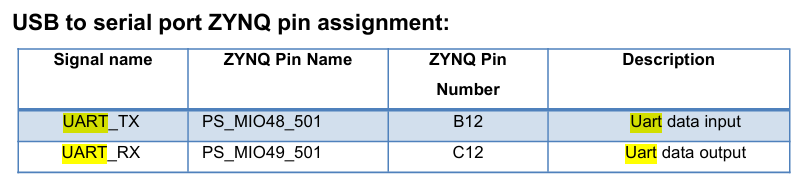

AX7010 FPGA 개발 보드는 USB to UART 칩으로 CP2102GM을 사용한다. USB 인터페이스는 Micro USB 인터페이스를 사용한다. UART의 TX/RX 신호는 Zynq EPP의 PS Bank501에 연결되며, 이 BANK의 VCCMIO의 전원이 1.8V로 설정되어 있고, CP2102GM은 3.3V이기 때문에 voltage level translator가 필요하다.

User Manual을 보면 UART는 두 개가 지원가능하다. UART_TX, RX가 각 Zynq에 연결된 PS pin name이 PS_MIO48_501/PS_MIO94_501 이므로 UART를 사용하면 이 핀을 사용할 것이다.

- Clock 설정

현재는 CPU 클럭 설정을 변경할 필요는 없다. 따라서 default 값인 33.3333MHz로 설정한다.

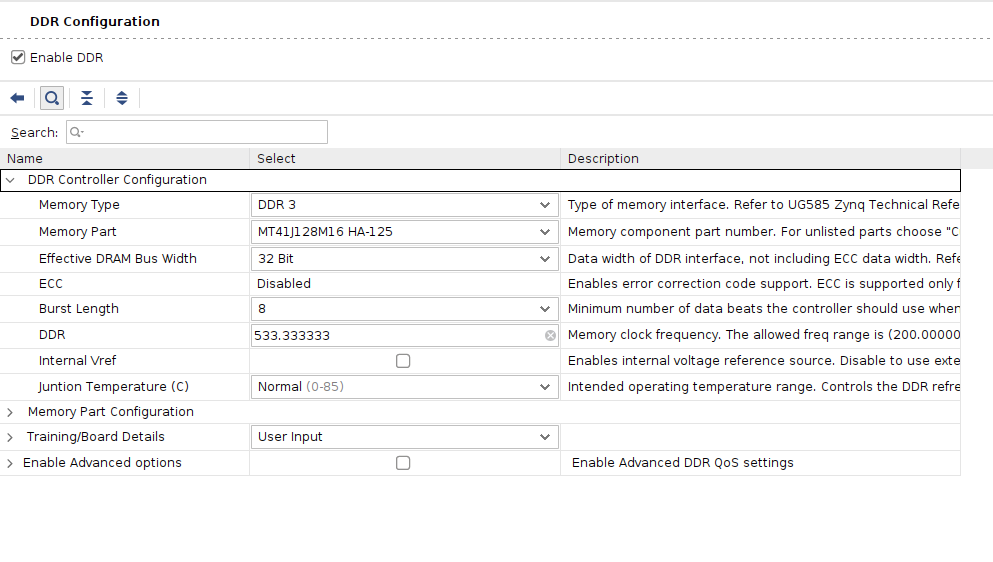

- DDR3 설정

DDR Configuration 탭에서, PS 터미널 ddr을 설정할 수 있다. AX7010은 DDR3 모델로 MT41J128M16 HA-125을 사용한다.

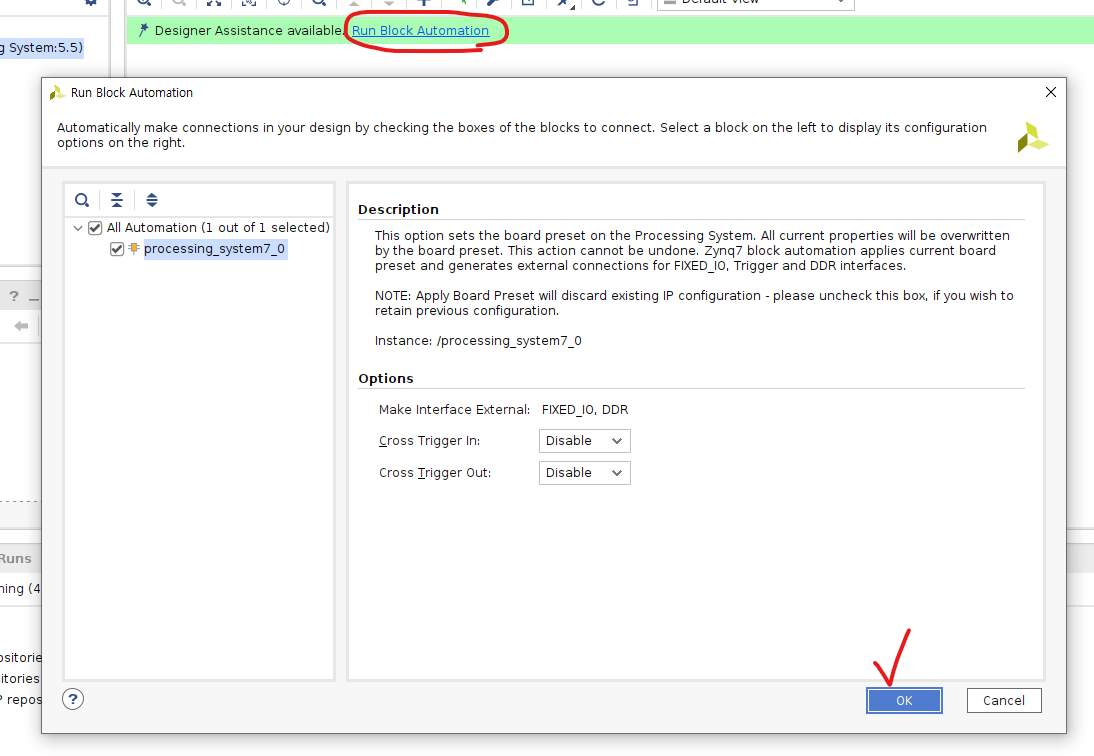

Run Block Automation을 실행한다.

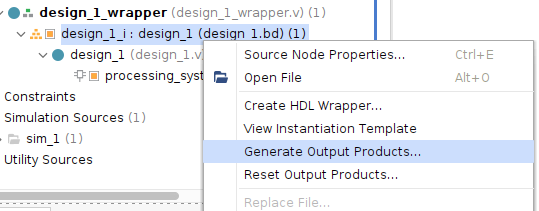

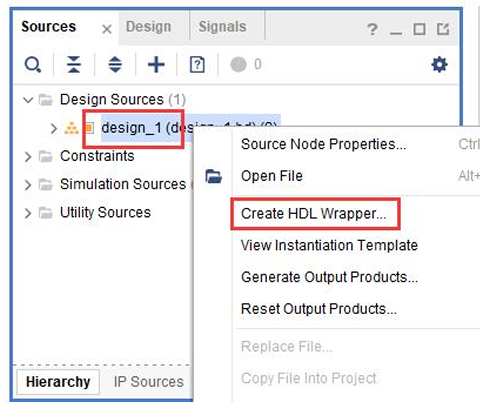

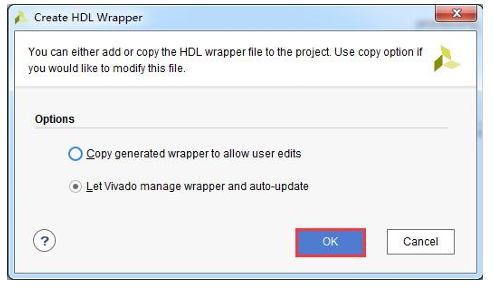

- Create HDL wrapper 선택.

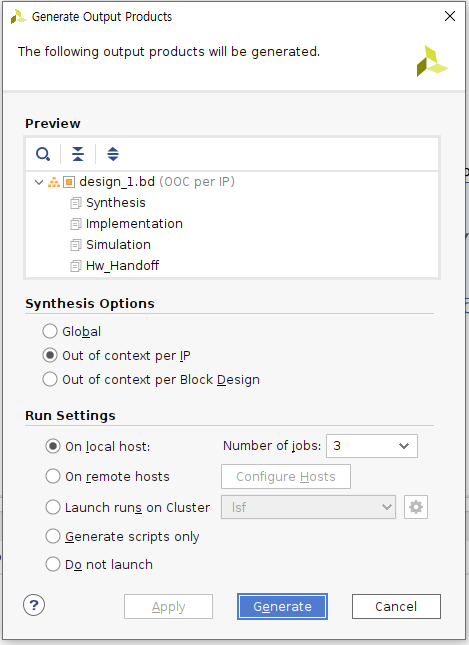

- Generate Output Products 실행.

이 단계는 block output file을 생성해 주는데, IP를 포함하여 instantiation 템플릿, RTL 소스 파일, XDC Constraints, third-party 통합 소스 파일 등을 포함해 결과물을 생성한다.